Rambus宣布推出业界首款HBM4控制器IP,加速下一代AI工作负载

基于一百多项HBM成功设计案例,确保芯片一次流片成功

在低延迟下提供超过HBM3两倍的吞吐量,满足生成式AI和高性能计算(HPC)工作负载的需求

扩展了业界领先的高性能内存解决方案的半导体IP产品组合

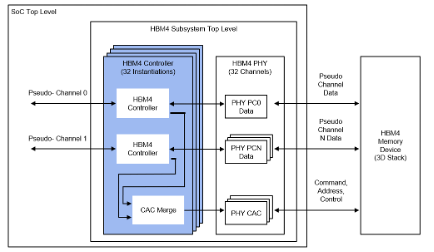

图1:Rambus HBM4控制器

中国北京,2024年11月13日 —— 作为业界领先的芯片和半导体IP供应商,致力于使数据传输更快更安全,Rambus Inc.(纳斯达克股票代码:RMBS)今日宣布推出业界首款HBM4内存控制器IP,凭借广泛的生态系统支持,扩展了其在HBM IP领域的市场领导地位。这一全新解决方案支持HBM4设备的高级功能集, 使设计人员能够应对下一代AI加速器和图形处理器(GPU)对内存带宽所提出的苛刻需求。

Rambus高级副总裁兼半导体IP部门总经理Matt Jones表示:“随着大语言模型(LLMs)的参数量已跨越万亿大关,并持续呈现增长态势,在此背景下,突破内存带宽与容量的固有瓶颈,对于满足AI在训练和推理过程中对实时性能的迫切需求,显得尤为关键。作为引领AI 2.0时代的半导体IP供应商,我们即将推出业界首款HBM4控制器IP解决方案,帮助客户在其最先进的处理器与加速器中实现性能的突破式提升。”

Cadence芯片解决方案事业部协议IP营销高级总监Arif Khan表示:“随着异构计算架构的规模不断扩展,以支持有着海量数据移动的多样化工作负载,HBM IP生态系统必须持续提升其性能,并推出可互操作的解决方案,以满足客户日益增长的需求。我们很高兴看到Rambus提供可互操作的HBM4控制器IP解决方案以支持生态系统,并与Cadence在HBM PHY和解决方案性能领域的领导地位相结合,共同推动行业向开始新一代HBM内存过渡。“

三星电子执行副总裁兼晶圆代工IP生态系统负责人Jongshin Shin表示,:“HBM4将代表生成式AI和其他HPC应用在内存技术方面的重大突破。确保HBM4 IP解决方案的可用性,对于为HBM4在市场上的广泛采用奠定坚实基础而言具有至关重要的意义。三星期待与Rambus及更广泛的生态系统密切合作,共同为AI新时代开发全新的HBM4解决方案。“

西门子EDA 副总裁兼设计验证技术总经理Abhi Kolpekwar表示:“在当前复杂多变且快速发展的半导体设计领域,预验证的IP解决方案对于实现芯片一次流片成功来说非常关键。Rambus与西门子之间建立的长期且成功的合作关系,一直致力于协助我们的共同客户达成其产品与商业目标。我们希望能够继续携手合作,推出新一代的、经西门子高质量验证IP验证的、一流的Rambus HBM4内存控制器。”

IDC使能技术和半导体集团副总裁Mario Morales表示:“HBM是AI的关键赋能技术。原因在于,AI处理器和加速器需依赖高性能、高密度的内存,以满足AI工作负载所带来的庞大计算需求。随着AI处理器和加速器的进步,它们也会需要HBM的进步。如今,市场上HBM4 IP的出现将作为一个不可或缺的赋能构建模块,为那些正致力于开发前沿AI硬件的设计人员提供支持。“

Rambus HBM4控制器支持新一代HBM内存部署,适用于尖端AI加速器、图形和HPC应用。HBM4控制器支持6.4 Gbps的JEDEC规范。Rambus HBM4控制器IP可与第三方或客户的PHY解决方案搭配使用,共同构建出完整的HBM4内存子系统。

供货情况和更多信息

Rambus HBM4控制器IP是Rambus领先的数字控制器解决方案组合中的最新产品。该控制器现已开放授权,早期设计客户可立即申请。

如需了解有关Rambus HBM4控制器IP的更多信息,请访问https://www.rambus.com/interface-ip/hbm/。

JEDEC正在制定HBM4内存标准。JEDEC标准在制定过程中和制定后可能会发生变化,包括被JEDEC董事会否决。